# 11-6 電界効果トランジスタ(Field Effect Transister: FET) 電界効果トランジスタ(ユニポーラ形トランジスタ)

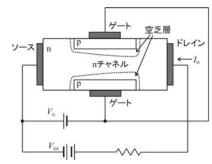

- ·ゲート電極: キャリアの流れを制御する(キャリアの通る道幅をコントロール)。

- **・ソース電極**: キャリアを放出する(キャリアを流す源)。

- ・ドレイン電極: キャリアを吸収する(キャリアが流れていく出口)。

- **・チャネル**: キャリアの通り道で、キャリアが電子なら「n チャネル」、正孔なら「p チャネル」。

ゲート電極がどの構造をしているかによって次のように分類される。

- ・pn 接合 → 接合型 FET(JFET)

- ・MS ショットキー接触 → Schottky Barrier FET(SBFET)、Metal Semiconductor FET(MESFET)

- ・MOS 接触 → MOS 形 FET、MIS 形 FET

## 11-6-1 接合型電界効果トランジスタ(JFET)

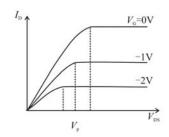

- ・ソース-ドレイン間電圧  $V_{DS}$  を増加すると、オームの法則に従ってドレイン電流  $I_D$  が直線的に増加する。

- ・ $V_{DS}$  を増加していくと空乏層が広がり、キャリアの通り道であるチャネルが狭くなり、次第に  $I_D$  が流れにくくなる(オームの法則からズレてくる)。

- $\cdot V_{\mathrm{DS}}$ をさらに増加すると、両ゲート側からの空乏層同士が接し、チャネルを閉じてしまう。この状態を**ピンチオフ(pinch-off)**といい、電圧値を**ピンチオフ電圧**  $V_{\mathrm{P}}$  という。このとき  $I_{\mathrm{D}}$  は飽和する。

- ・ $V_P$ 以上の電圧を加えても、チャネルの形は変化しないので  $I_D$  は一定となる。

- ・ゲート電圧  $V_{\rm G}$  に逆バイアスを印加すると、ピンチオフ状態が低い  $V_{\rm DS}$  でも生じるようになる。

Fig.1 JFET の構造

Fig.2 JFET の特性

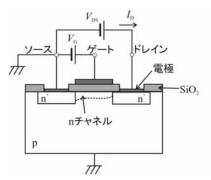

#### 11-6-3 MOS 電界効果トランジスタ(MOSFET)

#### エンハンスメント形(enhancement-mode)

ゲート電圧  $V_G=0$  でドレイン電流  $I_D$  がほとんど流れない。 ゲートに電圧を掛けることによって、ゲート下に反転層を形成してn チャネルをつくる。

### デプレッション形(depletion-mode)

不純物(ドナー)をドープして予めnチャネルを形成しているので、 $V_G = 0$ でも $I_D$ が流れる。

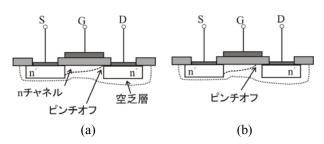

- ・ソース-ドレイン間電圧  $V_{\rm DS}$  が小さい場合は、反転層が一様にできるのでドレイン電流  $I_{\rm D}$  が直線的に増加する。

- ・ $V_{DS}$ を増加していくとドレイン側から空乏層が広がり(pn接合の逆バイアスのため)、チャネルが狭くなりピンチオフとなる(Fig.4(a))。

- ・ $V_{DS}$ をさらに増加すると、ピンチオフがソース側に広がり、電圧は空乏層にのみ掛かるため  $I_D$  は飽和する(Fig.4(b))。

Fig.3 MOSFET の構造

Fig.4 ピンチオフ状態