# 10 電界効果トランジスタ(Field Effect Transister : FET)

**電界効果トランジスタ(ユニポーラ形トランジスタ)**

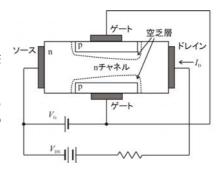

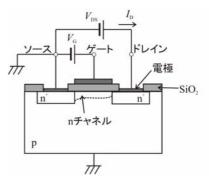

- ·ゲート電極: キャリアの流れを制御する(キャリアの通る道幅をコントロール)。

- **・ソース電極**: キャリアを放出する(キャリアを流す源)。

- **・ドレイン電極**: キャリアを吸収する(キャリアが流れていく出口)。

- **・チャネル**: キャリアの通り道で、キャリアが電子なら「n チャネル」、正孔なら「p チャネル」。

ゲート電極がどの構造をしているかによって次のように分類される。

- ・pn 接合 → 接合型 FET(JFET)

- ・MS ショットキー接触 → Schottky Barrier FET(SBFET)、Metal Semiconductor FET(MESFET)

- ・MIS(MOS)接触 → MIS 形 FET、MOS 形 FET

# 10-1 接合型電界効果トランジスタ(JFET)

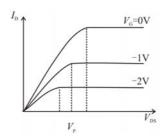

- ・ソース-ドレイン間電圧  $V_{DS}$  を増加すると、オームの法則に従ってドレイン電流  $I_D$  が直線的に増加する。

- ・ $V_{DS}$  を増加していくと空乏層が広がり、キャリアの通り道であるチャネルが狭くなり、次第に  $I_D$  が流れにくくなる(オームの法則からズレてくる)。

- ・ $V_{DS}$ をさらに増加すると、両ゲート側からの空乏層同士が接し、チャネルを閉じてしまう。この状態を**ピンチオフ**(pinch-off)といい、電圧値を**ピンチオフ電圧**  $V_P$  という。このとき  $I_D$  は飽和する。

- ・ $V_P$ 以上の電圧を加えても、チャネルの形は変化しないので  $I_D$  は一定となる。

- ・ゲート電圧  $V_{\rm G}$  に逆バイアスを印加すると、ピンチオフ状態が低い  $V_{\rm DS}$  でも生じるようになる。

Fig.1 JFET の構造

Fig.2 JFET の特性

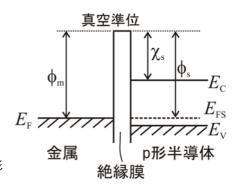

### 10-3 MIS 構造

## MIS: Metal-Insulator-Semiconductor

半導体表面に絶縁層を形成し、その上に金属電極をつけた構造(主に、絶縁層として、酸化膜が使われている)。

## MIS 構造を使ったデバイス

- ·MIS(MOS)トランジスタ

- ·MIS(MOS)FET

- ・電荷結合素子(CCD: Charge Coupled Devices)など

Fig.3 MIS 構造

## ○平衡時(V=0、理想状態)

## 理想状態

- ・金属と半導体の仕事関数が等しい

- ・絶縁体膜中に電荷がない

- ・絶縁体-半導体界面の界面準位が無視できる

- → バンドの曲がりがないと仮定する。

(実際の MIS 構造では V=0 でバンドの曲がりが存在する。この影響をなくすように掛ける電圧を「フラットバンド電圧」という)

Fig.4 平衡時

○*V* < 0 のとき

(n 形半導体の時は V > 0)

# 「**蓄積状態」**E<sub>F</sub> QV 蓄積層 Qs 正孔(+電荷) スター

$\bigcirc V > 0$  のとき

(n 形半導体の時は V < 0)

# 「空乏層状態」

Fig.6 空乏状態

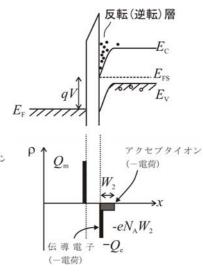

$\bigcirc V >> 0$  のとき

(n 形半導体の時は V << 0)

# 「反転(逆転)状態」

Fig.7 反転状態

正孔が酸化膜-半導体界面に集まり、多数キャリア密度が高くなる。

Fig.5 蓄積状態

→ 蓄積層が形成され、(横 方向に)大きな電流 Iが 流れ易くなる。 正孔は半導体内部へと移動し、 界面付近にアクセプタイオン が残る。

ightarrow 空乏層が形成され、電流Iは流れにくくなる。

フェルミ準位が伝導帯に近づ くと半導体表面が n 形に変化 し、伝導電子が現れる。

→ 反転層が形成され、電子 による(横方向の)電流 *I* が 流れ易くなる。

## 10-4 MIS 電界効果トランジスタ(MISFET)

# エン<u>ハンスメント形(enhancement-mode)</u>

ゲート電圧  $V_G=0$  でドレイン電流  $I_D$  がほとんど流れない。 ゲートに電圧を掛けることによって、ゲート下に反転層を形成してn チャネルをつくる。

# デプレッション形(depletion-mode)

不純物(ドナー)をドープして予めn チャネルを形成しているので、 $V_G = 0$  でも $I_D$ が流れる。

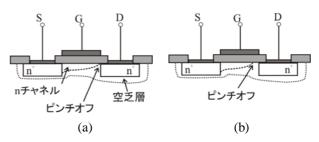

- ・ソース-ドレイン間電圧  $V_{DS}$  が小さい場合は、反転層が一様にできるのでドレイン電流  $I_D$  が直線的に増加する。

- ・ $V_{DS}$ を増加していくとドレイン側から空乏層が広がり(pn 接合の逆バイアスのため)、チャネルが狭くなりピンチオフとなる(Fig.9(a))。

- ・ $V_{DS}$ をさらに増加すると、ピンチオフがソース側に広がり、電圧は空乏層にのみ掛かるため  $I_D$  は飽和する(Fig.9(b))。

Fig.8 MISFET の構造

Fig.9 ピンチオフ状態